# REACTION WHEEL

5 Nms RW4-5.0

Interface Control Document

RL-TOR-ICD-00033 v1.0

**Brent Brakeboer**

### **Document History**

| Release<br>Version | Authors         | Date     | Description     |

|--------------------|-----------------|----------|-----------------|

| 1.0                | Brent Brakeboer | 24/11/13 | Initial release |

|                    |                 |          |                 |

### **Reference Documents**

| ID   | Document Number | Title          | Version |

|------|-----------------|----------------|---------|

| RD-1 | RW-5.0-MICD     | Mechanical ICD | 1.0     |

|      |                 |                |         |

# **Table of Contents**

| 1     | Scope                                 | 6  |

|-------|---------------------------------------|----|

| 2     | Mechanical                            | 7  |

| 2.1   | Remove Before Flight                  | 7  |

| 3     | Environmental                         | 8  |

| 3.1   | Storage                               | 8  |

| 3.2   | Thermal                               | 8  |

| 3.3   | Pressure                              | 8  |

| 3.4   | Vibration                             | 8  |

| 4     | Electrical                            | 9  |

| 4.1   | Architecture                          | 9  |

| 4.1.1 | Regenerative Braking                  | 9  |

| 4.2   | Connections                           | 9  |

| 4.2.1 | Primary Connector                     | 9  |

| 4.2.2 | Programming Header                    | 10 |

| 4.3   | Interface Specifications              | 10 |

| 4.3.1 | Power                                 | 10 |

| 4.3.2 | Address                               | 11 |

| 4.3.3 | Communications                        | 11 |

| 5     | Software                              | 13 |

| 5.1   | Protocol Layer 2 (Data Link Layer)    | 13 |

| 5.1.1 | Asynchronous Serial                   | 13 |

| 5.2   | Protocol Layer 3 (Network Layer)      | 13 |

| 5.2.1 | SLIP Encoding                         | 13 |

| 5.3   | Protocol Layer 4 (Transport Layer)    | 14 |

| 5.3.1 | Command and Reply                     | 14 |

| 5.3.2 | NSP Message Format                    | 14 |

| 5.3.3 | NSP Addresses                         | 14 |

| 5.3.4 | Wheel Address and Port Selection      |    |

| 5.3.5 | Message Control Fields                |    |

| 5.3.6 | Data Field                            |    |

| 5.3.7 | Message CRC                           |    |

| 5.3.8 | Error Conditions                      |    |

| 5.4   | Protocol Layer 5 (Session Layer)      |    |

| 5.4.1 | Operating Modes                       |    |

| 5.4.2 | Byte Order                            |    |

| 5.4.3 | Command Codes                         |    |

| 5.5   | Protocol Layer 6 (Presentation Layer) |    |

| 5.5.1 | Fault Handling                        |    |

| 5.5.2 | Memory Map                            |    |

| 5.5.3 | Diagnostics                           |    |

| 5.5.4 | EDAC Memory                           |    |

| 5.5.5 | Command Modes                         |    |

| 5.6   | Special Features                      |    |

| 5.6.1 | Virtual Oscilloscope                  |    |

| 5.6.2 | Inducing Processor Faults             | 41 |

| 5.6.3 Inducing Memory ECC e              | errors |    |

|------------------------------------------|--------|----|

| List of Figures                          |        |    |

| Figure 1: Power Architecture             |        | .9 |

| _                                        |        |    |

| List of Tables                           |        |    |

| Table 1: Allowable Temperature Range .   |        | .8 |

| Table 2: Primary Connector               |        | 10 |

| Table 3: Primary Connector Pin-out       |        | 10 |

| •                                        |        |    |

| Table 5: Address Specification           |        | 11 |

| Table 6: RS485 Specification             |        | 11 |

| Table 7: Asynchronous UART Configurati   | tion   | 13 |

| Table 8: SLIP Framing Special Characters | 5      | 13 |

| Table 9: NSP Message Fields              |        | 14 |

| Table 10: Default NSP Addresses          |        | 15 |

| Table 11: Message Control Field          |        | 16 |

| Table 12: Command Codes                  |        | 18 |

| Table 13: Command Format                 |        | 18 |

| Table 14: Reply Format                   |        | 19 |

| Table 15: Normal Command Format          |        | 19 |

| Table 16: Reboot Command Format          |        | 19 |

| Table 17: Normal Reply Format            |        | 19 |

| Table 18: Reboot Reply Format            |        | 19 |

| Table 19: Short Command Format           |        | 20 |

| Table 20: Long Command Format            |        | 20 |

| Table 21: Reply Format                   |        | 20 |

| Table 22: Command Format                 |        | 20 |

| Table 23: Reply Format                   |        | 21 |

| Table 24: Command Format                 |        | 21 |

| Table 25: Reply Format                   |        | 21 |

| Table 26: Diagnostic Result Structure Fo | rmat   | 21 |

| Table 27: Command Format                 |        | 21 |

| Table 28: Reply Format                   |        | 21 |

| Table 29: Command Format                 |        | 22 |

| Table 30: Reply Format                   |        | 22 |

| Table 31: Normal Reply Structure         |        | 22 |

| Table 32: Mode Reply Structure           |        | 22 |

| Table 33: Command and Reply Format    | 22 |

|---------------------------------------|----|

| Table 34: Normal Store Structure      | 23 |

| Table 35: Mode Store Structure        | 23 |

| Table 36: Normal Reply Structure      | 23 |

| Table 37: Mode Reply Structure        | 23 |

| Table 38: Short Command Format        | 23 |

| Table 39: Long Command Format         | 23 |

| Table 40: Reply Format                | 23 |

| Table 41: Command Format              | 24 |

| Table 42: Reply Format                | 24 |

| Table 43: Command Format              | 24 |

| Table 44: Gather Command Structure    | 24 |

| Table 45: Reply Format                | 24 |

| Table 46: Gather Result Structure     | 24 |

| Table 47: Processor Memory Map        | 25 |

| Table 48: Application Image Structure | 26 |

| Table 49: Diagnostic Channels         | 27 |

| Table 50: EDAC Memory Contents        | 28 |

| Table 51: Hall_Digital Bitfield       | 31 |

| Table 52: Flags_Active Bitfield       | 37 |

| Table 53: Faults_Mask Bitfield        | 37 |

| Table 54: Reset_Enable Bitfield       | 37 |

| Table 55: Command Modes               | 38 |

# 1 Scope

This document details the mechanical, electrical and software interfaces for the RW-5.0 reaction wheels. Available models are:

• RW4-5.0-28-RS485

# 2 Mechanical

A detailed mechanical ICD can be provided upon request that includes:

- Mass properties

- Dimensions

- Mechanical Interfaces

# 2.1 Remove Before Flight

The following items are removed before flight:

| Item                  | Remove?    | Notes                          |

|-----------------------|------------|--------------------------------|

| Kapton bearing covers | May remove | 1x Kapton tape pieces, protect |

|                       |            | bearings from debris on ground |

## 3 Environmental

### 3.1 Storage

The wheel must be stored in a clean environment to keep dust out of the bearings. The humidity must be kept low to prevent corrosion of the steel rotor. The wheel may be stored in a sealed bag with desiccant.

### 3.2 Thermal

The table below details the operational and survivable temperature range for the product.

Table 1: Allowable Temperature Range

| Criteria              | Range                       |

|-----------------------|-----------------------------|

| Survival Temperature  | -40°C to +100°C             |

| Operating Temperature | -30°C to +85°C at interface |

The temperature is defined as the temperature of the base plate in the nominal mounting configuration.

### 3.3 Pressure

The wheel will operate in sea-level atmosphere and in hard vacuum. It has not been qualified to operate at high altitude atmospheres, and should not be powered during ascent unless additional testing is performed to show that there is no danger of arcing.

All materials meet the standard outgassing requirements of TML < 1%, CVCM < 0.1%.

### 3.4 Vibration

The wheel is designed to survive typical launch environments. It has been qualified to NASA GEVS levels (14.1Grms for 2 minutes/axis).

### 4 Electrical

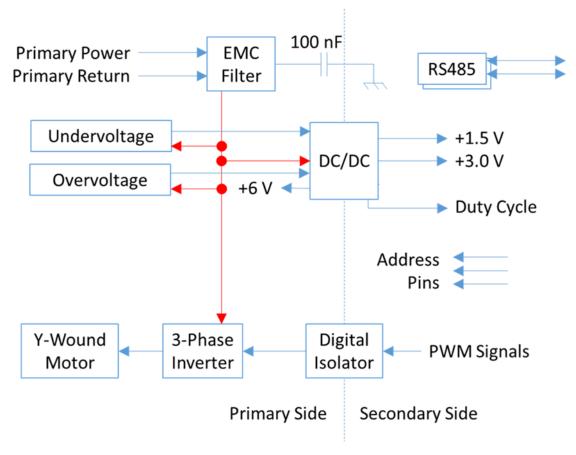

### 4.1 Architecture

Figure 1: Power Architecture

### 4.1.1 Regenerative Braking

The wheel makes use of regenerative braking when slowing the rotor under moderate torque. This will result in the wheel consuming a net negative amount of power, pushing current back out onto the spacecraft power bus. The spacecraft power system design must be able to accommodate this.

In an emergency, if the power line becomes disconnected from the power system (such as if turned off via a relay switch) regeneration will increase the voltage at the wheel until the overvoltage threshold is reached. This will cause the wheel to reset and cease regeneration.

### 4.2 Connections

### 4.2.1 Primary Connector

The wheel is fitted with a single 15-position micro-D socket receptacle. Note, where multiple contacts have the same pin name they are connected within the reaction wheel.

Table 2: Primary Connector

| Attribute                | Device Connector |

|--------------------------|------------------|

| Manufacturer             | Omnetics         |

| Manufacturer Part Number | A99089-015       |

| Specification            | MIL-DTL-83513    |

| Number of Contacts       | 15               |

| Gender                   | Female           |

Table 3: Primary Connector Pin-out

| Pin | Pin Name         | Signal Type          |

|-----|------------------|----------------------|

| 1   | Address 1        | Chassis or Open      |

| 2   | Address 2        | Chassis or Open      |

| 3   | Secondary Return | Chassis              |

| 4   | RS485_0_A        | RS485 Bus 0 – A Side |

| 5   | Secondary Return | Chassis              |

| 6   | Primary Return   | DC Power Return      |

| 7   | Primary Return   | DC Power Return      |

| 8   | Primary Power    | DC Power Input       |

| 9   | Address 0        | Chassis or Open      |

| 10  | RS485_1_B        | RS485 Bus 1 – B Side |

| 11  | RS485_1_A        | RS485 Bus 1 – A Side |

| 12  | RS485_0_B        | RS485 Bus 0 – B Side |

| 13  | Primary Return   | DC Power Return      |

| 14  | Primary Power    | DC Power Input       |

| 15  | Primary Power    | DC Power Input       |

### 4.2.2 Programming Header

This board implements a plug-of-nails style programming and debugging JTAG interface for development and programming purposes. This is a modified 10-pin JTAG port with FRAM power and WP override. This interface is not accessible once the RWA has been assembled.

# 4.3 Interface Specifications

This document only provides specifications for the primary power and communications interface. The factory JTAG interface will not be accessible after assembly.

#### 4.3.1 Power

**Table 4: Power Specification**

| Property                 | Value                                                      |

|--------------------------|------------------------------------------------------------|

| Nominal Primary Voltage  | +22 V to +34 V DC relative to primary return               |

| Absolute Maximum Voltage | -65 V to +63 V DC relative to primary return               |

| Isolation                | 100 nF in parallel with $1M\Omega$                         |

|                          | 100 V Hipot test permissible                               |

| Overvoltage threshold    | +52.6 V @ 25 C, 50 mV/K temperature variation, overvoltage |

|                          | shall be limited to 0.5s pulses at <10% duty cycle         |

| Undervoltage threshold   | +20.7 V Turn on, +14.5 V Turn off                          |

The power supply uses an undervoltage lockout (UVLO) circuit to prevent brownout behaviour at low input voltages. There is a large hysteresis on the limit to prevent oscillation. When the input voltage is too low, the DC/DC converter is inhibited and no power will reach the secondary circuits. The startup regulator and oscillator will remain active, so a modest input current will remain.

The power supply uses an overvoltage limit circuit to prevent damage from very high bus voltages. This circuit is implemented with a simple Zener diode, and thus has a significant temperature variation – the limit voltage increases with increasing temperature. There is no hysteresis on the limit, and so chatter may be possible. Activation of this circuit should only happen in an emergency, so this is considered acceptable. The startup regulator and oscillator remain active in an overvoltage condition. In this case the power dissipated in the startup linear regulator can become significant: maybe 10 mA across a 45 V drop. The startup regulator does not have overtemperature protection, so the time spent in the overvoltage condition must be strictly limited.

#### 4.3.1.1 Primary Return

The Primary Return (DC Power Return signal) is the return for the Primary Power (DC power input signal).

#### 4.3.1.2 Secondary Return (Chassis)

Secondary Return (Chassis) is the reference for all other signals. The secondary return is isolated from the primary return by a 1 Mohm resistor.

#### 4.3.2 Address

The address inputs allow the network address of the wheel to be set. Inputs must either be left open-circuit (digital '1') or connected to Secondary Return (digital '0'). The wheel will determine its address only once, at power-on.

Table 5: Address Specification

| Property                 | Value                                     |

|--------------------------|-------------------------------------------|

| Absolute Maximum Voltage | +/- 30 V DC, relative to secondary return |

| Input Resistance         | 4.75 kΩ                                   |

| Pull-up Resistance       | 40 kΩ                                     |

#### 4.3.3 Communications

The device has two RS485 transceivers. They may be used as two half-duplex 2-wire buses, or used together as a 4-wire bus. As a 4-wire bus, the wheel is interoperable with legacy RS422 signals.

Table 6: RS485 Specification

| Property                     | Value                                       |

|------------------------------|---------------------------------------------|

| Absolute Maximum Voltage     | -9 V to +13 V, relative to secondary return |

| Polarity                     | B > A in Mark (Idle) state                  |

|                              | A > B in Space (ON) state                   |

| Differential Output Voltage  | $>$ 1.5 V into 54 $\Omega$ termination      |

| Short-circuit Output Current | 250 mA max                                  |

| Input Differential Threshold | -0.20 V to -0.01 V                          |

| Input resistance             | > 48 kΩ each signal                         |

| ESD Rating                   | ±20 kV HBM (IEC 61000-4-2)                  |

There is no provision for termination inside the wheel. If it is needed, it should be spliced into the harness at the ends of the bus. For a spacecraft with short, slow RS485 buses it is typically not required or useful.

### 5 Software

### 5.1 Protocol Layer 2 (Data Link Layer)

### 5.1.1 Asynchronous Serial

The RS485 communications ports use an asynchronous serial protocol. The parameters are programmed into the unit bootloader at the factory, and special-order units with different parameters are available.

Table 7: Asynchronous UART Configuration

|                    | Hex value                   |

|--------------------|-----------------------------|

| Data Bits per Byte | 8                           |

| Parity             | None                        |

| Stop Bits          | 1                           |

| Nominal Baud Rate  | 115200, (230400 at request) |

Each word begins with a start bit with space (0) value. Eight data bits follow, with the LSB sent first and the MSB last. Finally, a stop bit is sent with mark (1) value. Once the stop bit has concluded the output transmitter may be disabled if there are no further words to follow.

### 5.2 Protocol Layer 3 (Network Layer)

NSP is the Nanosatellite Protocol, originally developed at UTIAS/SFL for use on the CanX nanosatellites. This in turn is descended from the Simple Serial Protocol (SSP) used by UTIAS/SFL and Dynacon on the MOST and CHIPSAT spacecraft as well as the Dynacon reaction wheels in the wider market.

The reaction wheel uses NSP messages for all communication.

### 5.2.1 SLIP Encoding

NSP messages are encoded for transmission on asynchronous or I2C serial channels use SLIP framing, as described in RFC 105. This is required in order to indicate the beginning and end of NSP messages.

**Table 8: SLIP Framing Special Characters**

|       | Hex value |

|-------|-----------|

| FEND  | 0xC0      |

| FESC  | 0xDB      |

| TFEND | 0xDC      |

| TFSEC | 0xDD      |

Each NSP message is transmitted with a FEND character added to the beginning and end. Whenever FEND would occur within the message it is replaced by two bytes: FESC TFEND. Whenever FESC would occur within the message it is replaced by FESC TFESC.

### 5.3 Protocol Layer 4 (Transport Layer)

### 5.3.1 Command and Reply

The wheel generates telemetry messages in response to command messages received. In the usual case, a single telemetry message will be sent as quickly as possible after reception of the command.

Some commands will take a period of time to execute and will only generate a telemetry message when they are complete. The wheel should be considered to own the communications bus while such a command is executed, so do not send additional commands to it or any other unit until the reply is complete.

While some NSP devices can generate multiple telemetry messages in response to a single command, the wheel will not. The P/F bit will be set for all replies, indicating that they are stand-alone final messages.

Notwithstanding the above, the wheel will not generate messages that are not linked to a command. The host spacecraft must poll it to determine its status and to read telemetry

### 5.3.2 NSP Message Format

Table 9: NSP Message Fields

| Length          | Field                 |

|-----------------|-----------------------|

| 1 byte          | Destination Address   |

| 1 byte          | Source Address        |

| 1 byte          | Message Control Field |

| 0 or more bytes | Data Field            |

| 2 bytes         | Message CRC           |

Each NSP message has the format shown above. The shortest possible messages are 5 bytes (with zero data, not counting framing).

The wheel supports a maximum data length of 260 bytes, giving a total message length of 265 bytes. Note that network-layer framing may add additional bytes to the message as it is transmitted.

#### 5.3.3 NSP Addresses

All NSP messages contain a destination and a source address. A reply message will be sent with a destination address equal to the source address of its command message. Similarly, the source address will be set equal to the destination address from the command.

The user is free to pick one or more NSP addresses for flight computers and other units that may talk to the wheel. Avoid choosing the SLIP framing characters FEND (0xC0) and FESC (0xDB), as well as the reserved address 0x00. By convention the flight computer would normally use NSP address 0x11.

The wheel pays no particular attention to the source address of commands, and will accept commands from any unit on the bus.

#### 5.3.4 Wheel Address and Port Selection

The wheel bootloader may support incoming communication on a number of communication ports: potentially up to two RS485 ports. In addition, there may be cases where outgoing reply packets are sent on a different port from the

command packet. For example, a 4-wire RS485 link can be implemented by receiving commands on one 2-wire RS485 port and sending replies on a different 2-wire RS485 port.

A wheel may respond to different NSP addresses on different ports. On any given port, incoming commands with different NSP addresses may cause replies to be issued on different ports.

The RW4 has two NSP state machines, and can handle simultaneous interactions on both ports. There are two possible contention situations:

- If a reply is generated on a port that is currently receiving an incoming message, the incoming message is abandoned and the reply is sent out. This probably results in an RS485 bus contention.

- If a reply is generated on a port that is already sending out a reply, the reply in progress is not interrupted. The new reply is abandoned there is no attempt to queue it.

Contention should not occur in a well-managed spacecraft.

The wheel uses the following NSP addresses:

Table 10: Default NSP Addresses

| Address 0 | Address 1 | Address 2 | NSP Address | Command Port | Telemetry Port |

|-----------|-----------|-----------|-------------|--------------|----------------|

| Short     | Short     | Short     | 0x40        | RS485_0      | RS485_1        |

| Short     | Short     | Short     | 0x50        | RS485_1      | RS485_1        |

| Short     | Short     | Short     | 0x60        | RS485_0      | RS485_0        |

| Short     | Short     | Short     | 0x70        | RS485_1      | RS485_0        |

| Open      | Short     | Short     | 0x41        | RS485_0      | RS485_1        |

| Open      | Short     | Short     | 0x51        | RS485_1      | RS485_1        |

| Open      | Short     | Short     | 0x61        | RS485_0      | RS485_0        |

| Open      | Short     | Short     | 0x71        | RS485_1      | RS485_0        |

| Short     | Open      | Short     | 0x42        | RS485_0      | RS485_1        |

| Short     | Open      | Short     | 0x52        | RS485_1      | RS485_1        |

| Short     | Open      | Short     | 0x62        | RS485_0      | RS485_0        |

| Short     | Open      | Short     | 0x72        | RS485_1      | RS485_0        |

| Open      | Open      | Short     | 0x43        | RS485_0      | RS485_1        |

| Open      | Open      | Short     | 0x53        | RS485_1      | RS485_1        |

| Open      | Open      | Short     | 0x63        | RS485_0      | RS485_0        |

| Open      | Open      | Short     | 0x73        | RS485_1      | RS485_0        |

| Short     | Short     | Open      | 0x44        | RS485_0      | RS485_1        |

| Short     | Short     | Open      | 0x54        | RS485_1      | RS485_1        |

| Short     | Short     | Open      | 0x64        | RS485_0      | RS485_0        |

| Short     | Short     | Open      | 0x74        | RS485_1      | RS485_0        |

| Open      | Short     | Open      | 0x45        | RS485_0      | RS485_1        |

| Open      | Short     | Open      | 0x55        | RS485_1      | RS485_1        |

| Open      | Short     | Open      | 0x65        | RS485_0      | RS485_0        |

| Open      | Short     | Open      | 0x75        | RS485_1      | RS485_0        |

| Short     | Open      | Open      | 0x46        | RS485_0      | RS485_1        |

| Short     | Open      | Open      | 0x56        | RS485_1      | RS485_1        |

| Short     | Open      | Open      | 0x66        | RS485_0      | RS485_0        |

| Short     | Open      | Open      | 0x76        | RS485_1      | RS485_0        |

| Open      | Open      | Open      | 0x47        | RS485_0      | RS485_1        |

| Open      | Open      | Open      | 0x57        | RS485_1      | RS485_1        |

| Open      | Open      | Open      | 0x67        | RS485_0      | RS485_0        |

| Open | Open | Open | 0x77 | RS485 1  | RS485 O  |

|------|------|------|------|----------|----------|

| Open | Open | Орсп | OA77 | 113403_1 | 113403_0 |

Short = Address pin shorted to Secondary Return in the harness

Open = Address pin left unconnected

In the normal spacecraft configuration with four reaction wheels, it is advised that the following addresses be used:

- X1

- X2

- X4

- X7

In the event of a failure of any one address input pin or harness straps the wheel will go to one of these addresses:

- X0

- X3

- X5

- X6

Thus, a single failure will never place two wheels at identical addresses.

### 5.3.5 Message Control Fields

Table 11: Message Control Field

| Bit     | Description      |

|---------|------------------|

| 7 (MSB) | "Poll/Final" Bit |

| 6       | "B" Bit          |

| 5       | "ACK" Bit        |

| 4-0     | Command Code     |

The message control field packs four values into a single byte. The command code is an enumerated value between 0x00 and 0x1F that determines how the data field should be interpreted.

The "ACK" bit is ignored on commands coming into the wheel. On telemetry reply messages sent by the wheel it is set to indicate successful execution of the command, or cleared to indicate that the command cannot be executed.

The "B" bit is copied unchanged from a command message into its reply message. The wheel does not use it internally.

The "Poll/Final" bit is interpreted differently for command and telemetry messages. For a command, the bit is "Poll". If it is set to '1' then the wheel will generate a telemetry message in reply. If it is cleared to '0' then the command will be executed, but no response telemetry message will be sent.

For a telemetry message, the bit is "Final". If a reply consists of a single telemetry message, then the bit is set to '1'. If a reply is too large to fit into a single message then the final message has the bit set to '1' and the others have the bit cleared to '0'.

#### 5.3.6 Data Field

The interpretation of the data field is dependent on the command code in the message control field. Some command codes may have no data, some may require a certain fixed number of data bytes, and some can accept a variable data length.

### 5.3.7 Message CRC

Each NSP message contains a 2 byte (16-bit) CRC to guard against errors in transmission. The 16-bit CCITT polynomial is used:  $x^16 + x^12 + x^5 + 1$ . The initial shift register value is 0xFFFF. Bytes are fed into the CRC computation starting with the destination address, and concluding with the last byte of the data field. Within a byte, bits are fed in LSB first.

The following fragment of C code, courtesy of Henry Spencer, illustrates how the CRC can be computed.

```

#define POLY 0x8408 /* bits reversed for LSB-first */

unsigned short crc = 0xffff;

while (len-- > 0) {

unsigned char ch = *bufp++;

for (i = 0; i < 8; i++) {

crc = (crc >> 1) ^ ( ((ch ^ crc) & 0x01) ? POLY : 0 );

ch >>= 1;

}

}

```

#### 5.3.8 Error Conditions

The wheel will ignore NSP command messages where the destination address does not correspond to its own NSP address. NSP messages with invalid CRC, invalid encapsulation, too short or too long are also ignored. In none of these cases will any reply message be generated.

If an NSP command message is in error due to an unknown command code, or if the data field is not consistent with the requirements of the command code, and if the "Poll" bit is set, then a NACK reply message will be generated. This message will be the same length as the command message, and contain the same data field. The command code will be the same, as will the "B" bit. The "ACK" bit will be cleared to '0'.

### 5.4 Protocol Layer 5 (Session Layer)

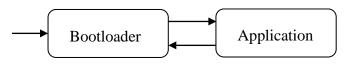

### 5.4.1 Operating Modes

Power-on starts the unit in bootloader mode.

Figure 2: Mode Transition Diagram

#### 5.4.1.1 Bootloader to Application Transition

The wheel will transition from bootloader to application mode upon receipt of an "INIT 0x20050000" command.

#### 5.4.1.2 Application to Bootloader Transition

Any transition from application mode to bootloader mode is accomplished through a processor reset. Reset is caused by the following conditions:

- An undervoltage is detected on Primary Power

- An overvoltage is detected on Primary Power

- An "INIT" command with no data is received.

- An exception or unexpected interrupt occurs

### 5.4.2 Byte Order

All multi-byte values transported in the data field of NSP messages are in little-endian format. That is, the least-significant byte is stored first, and the most-significant byte is stored last.

#### 5.4.3 Command Codes

Table 12: Command Codes

| Hex Value | Command     | Bootloader | Application |

|-----------|-------------|------------|-------------|

| 0x00      | PING        | Yes        | Yes         |

| 0x01      | INIT        | Yes        | Yes         |

| 0x02      | PEEK        | Yes        | Yes         |

| 0x03      | POKE        | Yes        | Yes         |

| 0x04      | DIAGNOSTIC  | Yes        | Yes         |

|           |             |            |             |

| 0x06      | CRC         | Yes        | Yes         |

| 0x07      | READ FILE   | No         | Yes         |

| 0x08      | WRITE FILE  | No         | Yes         |

| 0x09      | READ EDAC   | No         | Yes         |

| 0x0A      | WRITE EDAC  | No         | Yes         |

| 0x0B      | GATHER EDAC | No         | Yes         |

The table above shows the command codes that can be used by the host spacecraft to communicate with the wheel.

#### 5.4.3.1 Ping (0x00)

The PING command is typically used during testing to verify communications. Incoming data is ignored. The reply packet contains a human-readable text string containing:

- The type of device and the manufacturer

- The name, version and build of the software that is currently running on the target processor.

Table 13: Command Format

| Byte        | Description                                   |

|-------------|-----------------------------------------------|

| Bytes 0 – N | Zero or more bytes, ignored by the NSP module |

Table 14: Reply Format

| Byte        | Description                                       |

|-------------|---------------------------------------------------|

| Bytes 0 – N | Human-readable ASCII string. No NULL termination. |

#### 5.4.3.2 INIT (0x01)

The INIT command is used to change the operating mode of a wheel. In all cases, if a reply has been requested ("Poll" bit set to '1') then the reply will be sent before the processor state is changed.

The wheel will respond to an INIT with no data by completely resetting the device, returning to bootloader mode. If it is in bootloader mode, it will respond to an INIT with 4 bytes of data by running an Application Module at the corresponding address.

As a special case, the command INIT 0xDEADBEEF is used once in the factory to write-protect the bootloader FRAM. The bootloader FRAM can only be unlocked by issuing a POKE while the /WP pin on the test connector is held high.

An INIT command with an address will be NACKed if the device is not in bootloader mode.

An INIT command with an address in the bootloader or user FRAM will cause an application image to be loaded from FRAM into RAM (see application image section for format). Once the application has been loaded, the processor will branch to the specified starting point and run the program. In the special case where the starting point is zero, no jump will be made and the processor will remain in bootloader mode.

An INIT command with an address in either RAM area will cause a program branch to that address. It is assumed that a program resides at that address: either copied from FRAM by a previous command, or loaded from the first 128 kB of bootloader FRAM on a reset, or loaded directly from a series of POKEs.

Table 15: Normal Command Format

| Byte        | Description                                |

|-------------|--------------------------------------------|

| Bytes 0 – 3 | 32-bit integer address of program to start |

Table 16: Reboot Command Format

| Byte | Description      |

|------|------------------|

|      | No payload bytes |

Table 17: Normal Reply Format

| Byte        | Description                                     |

|-------------|-------------------------------------------------|

| Bytes 0 – 3 | 32-bit integer address of program to be started |

Table 18: Reboot Reply Format

| Byte | Description      |

|------|------------------|

|      | No payload bytes |

#### 5.4.3.3 PEEK (0x02)

The PEEK command is used to read the device memory. Short and long formats of this command are available for historical reasons. Short commands can be distinguished from long commands by their lengths.

PEEK access to FRAM can be of any length, and without alignment restriction, provided it does not cross the boundary from bootloader FRAM to user FRAM. PEEKs to other memory areas must obey one of the following restrictions:

- Length = 1

- Length = 2, aligned to even address

- Length = 4\*N, aligned to multiple of 4

PEEKs to unimplemented memory locations may be expected to generate hardfault exceptions

Table 19: Short Command Format

| Byte        | Description                                                                    |

|-------------|--------------------------------------------------------------------------------|

| Bytes 0 – 3 | 32-bit address to start peeking data                                           |

| Byte 4      | Number of bytes to read. A value of 0 indicates that 256 bytes should be read. |

Table 20: Long Command Format

| Byte        | Description                          |

|-------------|--------------------------------------|

| Bytes 0 – 3 | 32-bit address to start peeking data |

| Byte 4 – 5  | Number of bytes to read.             |

Table 21: Reply Format

| Byte        | Description                                   |

|-------------|-----------------------------------------------|

| Bytes 0 – 3 | 32-bit address of the start of data           |

| Bytes 4 – N | One or more bytes read from the target memory |

#### 5.4.3.4 POKE (0x03)

The POKE command is used to write the device memory.

POKE access to FRAM can be of any length, and without alignment restriction, provided it does not cross the boundary from bootloader FRAM to user FRAM. POKEs to other memory areas must obey one of the following restrictions:

- Length = 1

- Length = 2, aligned to even address

- Length = 4\*N, aligned to multiple of 4

POKEs to unimplemented memory locations may be expected to generate hardfault exceptions. POKEs to write-protected FRAM will not generate any sort of error return, but the target memory will not be altered.

Table 22: Command Format

| Byte        | Description                                 |

|-------------|---------------------------------------------|

| Bytes 0 – 3 | 32-bit address to start poking data         |

| Bytes 4 – N | 1 - 256 bytes to write to the target memory |

Table 23: Reply Format

| Byte        | Description                                |

|-------------|--------------------------------------------|

| Bytes 0 – 3 | 32-bit address where data write began      |

| Bytes 4 – N | 1 – 256 bytes written to the target memory |

#### 5.4.3.5 DIAGNOSTIC (0x04)

The DIAGNOSTIC command gathers error count data from the wheel.

Table 24: Command Format

| Byte        | Description                                                    |

|-------------|----------------------------------------------------------------|

| Bytes 0 – N | Address of the diagnostic channel to read, as an 8-bit integer |

Table 25: Reply Format

| Byte        | Description                                      |

|-------------|--------------------------------------------------|

| Bytes 0 – N | List of one or more diagnostic result structures |

Table 26: Diagnostic Result Structure Format

| Byte        | Description                                                                |

|-------------|----------------------------------------------------------------------------|

| Byte 0      | Address of the diagnostic channel read, as an 8-bit integer                |

| Bytes 1 – 4 | Diagnostic value from the addressed channel, generally as a 32-bit integer |

#### 5.4.3.6 CRC (0x06)

CRC command is used to calculate a checksum on an area of flash memory. The CRC uses the same 16-bit polynomial, with the same bit order, as is used for NSP messages.

CRC addresses are not restricted as to alignment, for any of the memory areas. A CRC must not cover both bootloader FRAM and user FRAM. CRC access to unimplemented memory can be expected to generate hardfault exceptions.

The CRC command can potentially be used to request the CRC of the wheel's entire memory. The worst case would be the CRC of a 256 kB FRAM chip which takes 340 msec from command to reply (assuming no additional realtime processor load from the application program). The application control loop may be stalled during this time, preventing fine speed control.

Table 27: Command Format

| Byte        | Description                                        |

|-------------|----------------------------------------------------|

| Bytes 0 – 3 | Address of the first byte to CRC as 32-bit integer |

| Bytes 4 – 7 | Address of the last byte to CRC as 32-bit integer  |

Table 28: Reply Format

| Byte        | Description                                        |

|-------------|----------------------------------------------------|

| Bytes 0 – 3 | Address of the first byte in CRC as 32-bit integer |

| Bytes 4 – 7 | Address of the last byte in CRC as 32-bit integer  |

| Byte        | Description                  |

|-------------|------------------------------|

| Bytes 8 – 9 | CRC result as 16-bit integer |

#### 5.4.3.7 READ FILE (0x07)

The Read File command returns one or more "files", which are four consecutive bytes of EDAC protected memory. A read from address 0 is a special case, and an additional mode byte is returned.

Note that because of the single byte of addressing, not all of the EDAC memory can be accessed by this command.

When multiple telemetry files are read by a single command, they are guaranteed to be internally consistent (i.e. from the same control frame). Files can be read in any order, and a single file can be read multiple times.

Table 29: Command Format

| Byte    | Description                                                          |

|---------|----------------------------------------------------------------------|

| Bytes 0 | EDAC address divided by 4 (0 – 255). 0 for mode, 1 – 255 for normal. |

Table 30: Reply Format

| Byte        | Description                                                                          |

|-------------|--------------------------------------------------------------------------------------|

| Bytes 0 – N | List of File Reply structures. The first byte of each structure determines its type. |

Table 31: Normal Reply Structure

| Byte        | Description                                  |

|-------------|----------------------------------------------|

| Byte 0      | Non-zero EDAC address divided by 4 (1 – 255) |

| Bytes 1 – 4 | EDAC data bytes read from memory             |

Table 32: Mode Reply Structure

| Byte        | Description                  |

|-------------|------------------------------|

| Byte 0      | 0                            |

| Byte 1      | Command type read from EDAC  |

| Bytes 2 – 5 | Command value read from EDAC |

#### 5.4.3.8 WRITE FILE (0x08)

The Write File command stores one "files", which are four consecutive bytes of EDAC protected memory. A write to address 0 is a special case, and an additional mode byte is stored.

Note that because of the single byte of addressing, not all of the EDAC memory can be accessed by this command.

When multiple parameter files are written by a single command, they are guaranteed to be internally consistent (i.e. into the same control frame). Files can be written in any order, and a single file can be written multiple times.

If a Write File command fails due to improper formatting then no modification to EDAC memory is made.

Table 33: Command and Reply Format

| Byte        | Description                                                                            |

|-------------|----------------------------------------------------------------------------------------|

| Bytes 0 – N | List of File Store (Reply) structures. The first byte of each structure determines its |

|             | type.                                                                                  |

Table 34: Normal Store Structure

| Byte        | Description                                  |

|-------------|----------------------------------------------|

| Byte 0      | Non-zero EDAC address divided by 4 (1 – 255) |

| Bytes 1 – 4 | Data bytes to write to EDAC memory           |

Table 35: Mode Store Structure

| Byte        | Description            |

|-------------|------------------------|

| Byte 0      | 0                      |

| Byte 1      | Command type to store  |

| Bytes 2 – 5 | Command value to store |

Table 36: Normal Reply Structure

| Byte        | Description                                  |

|-------------|----------------------------------------------|

| Byte 0      | Non-zero EDAC address divided by 4 (1 – 255) |

| Bytes 1 – 4 | EDAC data bytes read from memory             |

Table 37: Mode Reply Structure

| Byte        | Description                  |

|-------------|------------------------------|

| Byte 0      | 0                            |

| Byte 1      | Command type read from EDAC  |

| Bytes 2 – 5 | Command value read from EDAC |

#### 5.4.3.9 READ EDAC (0x09)

The Read EDAC command returns bytes from EDAC memory. The read process is atomic. Long and short command formats are available.

Table 38: Short Command Format

| Byte        | Description                                                                    |

|-------------|--------------------------------------------------------------------------------|

| Bytes 0 – 1 | EDAC address to start reading                                                  |

| Byte 2      | Number of bytes to read. A value of 0 indicates that 256 bytes should be read. |

Table 39: Long Command Format

| Byte        | Description                   |

|-------------|-------------------------------|

| Bytes 0 – 1 | EDAC address to start reading |

| Bytes 2 – 3 | Number of bytes to read.      |

Table 40: Reply Format

| Byte        | Description                          |

|-------------|--------------------------------------|

| Bytes 0 – 1 | EDAC address where reading started   |

| Bytes 2 – N | The data bytes read from EDAC memory |

#### 5.4.3.10 WRITE EDAC (0x0A)

The Write EDAC command writes bytes into EDAC memory. The write process is atomic.

Table 41: Command Format

| Byte        | Description                        |  |  |

|-------------|------------------------------------|--|--|

| Bytes 0 – 1 | EDAC address to start reading      |  |  |

| Bytes 2 – N | Data bytes to write to EDAC memory |  |  |

Table 42: Reply Format

| Byte        | Description                           |  |  |

|-------------|---------------------------------------|--|--|

| Bytes 0 – 1 | EDAC address where reading started    |  |  |

| Bytes 2 – N | The data bytes written to EDAC memory |  |  |

#### 5.4.3.11 GATHER EDAC (0x0B)

The Gather EDAC command allows multiple separate ranges of EDAC memory to be read in an atomic manner.

Table 43: Command Format

| Byte        | Description                       |  |  |

|-------------|-----------------------------------|--|--|

| Bytes 0 – N | List of gather command structures |  |  |

Table 44: Gather Command Structure

| Byte        | Description                   |  |  |

|-------------|-------------------------------|--|--|

| Bytes 0 – 1 | EDAC address to start reading |  |  |

| Bytes 2 – 3 | Number of bytes to read       |  |  |

Table 45: Reply Format

| Byte        | Description                      |  |  |

|-------------|----------------------------------|--|--|

| Bytes 0 – N | List of gather result structures |  |  |

Table 46: Gather Result Structure

| Byte        | Description                        |  |  |

|-------------|------------------------------------|--|--|

| Bytes 0 – 1 | EDAC address where reading started |  |  |

| Bytes 2 – 3 | Number of bytes read               |  |  |

| Bytes 4 – N | Data bytes                         |  |  |

### 5.5 Protocol Layer 6 (Presentation Layer)

### 5.5.1 Fault Handling

The application program can detect several different fault conditions:

- Over temperature and under temperature

- Rotor overspeed

- Motor overcurrent

- · Hall sensor error

- · Temperature delta

For all faults, except hall sensor error, the fault threshold (temperature, speed, current) can be adjusted. A Hall sensor error is declared when the HALL\_IMPOSSIBLE or HALL\_SKIP count increments. Each of these fault conditions sets a unique fault flag. Each fault can be masked.

If an unmasked fault occurs, the motor drive is turned off. The rotor will slowly coast to a halt under friction alone.

The user can detect a fault by reading FLAGS\_ACTIVE. The user can clear a fault by writing '0' to the corresponding fault flag. Once all fault flags are clear or masked, the wheel will resume normal function.

Users are cautioned against clearing or masking faults without understanding the cause. The fault logic exists to protect the hardware. For example, running at high torque with the overtemperature faults masked risks damaging the motor from overheat.

### 5.5.2 Memory Map

Table 47: Processor Memory Map

| Address Range           | Function                  |

|-------------------------|---------------------------|

| 0x00000000 - 0x0003FFFB | Program RAM               |

| 0x0003FFFC - 0x0003FFFF | Program RAM ECC trap word |

| 0x20000000 - 0x2003FFFF | Bootloader FRAM           |

| 0x20040000 - 0x2007FFFF | User FRAM                 |

| 0x40000000 - 0x4002F000 | Hardware registers        |

| 0x5FFF8000 – 0x5FFFFFFB | Data RAM0                 |

| 0x5FFFFFFC – 0x5FFFFFFF | Data RAM0 ECC trap word   |

| 0x60000000 - 0x60007FFB | Data RAM1                 |

| 0x60007FFC - 0x60007FFF | Data RAM1 ECC trap word   |

The supervisor memory can be directly accessed with PEEK and POKE commands, and CRCs calculated with CRC commands. It is represented as a single 32-bit memory space, sparsely populated.

Note that the memory-map used for the serial commands differs from the internal CPU memory map, to accommodate the FRAM. This is mapped at address 0x20000000 for compatibility with existing tooling. The CPU memory at that address internally has been remapped to 0x60000000.

#### 5.5.2.1 Program RAM

Code is executed from this memory. At reset the first 256 kB of bootloader FRAM is copied into program RAM.

#### 5.5.2.2 Data RAM

Data RAM0 is used for bootloader and stack. It is cleared to 0 at power-up and after a reset. Data RAM1 is free for application data.

#### 5.5.2.3 Bootloader FRAM

This non-volatile memory is programmed at the factory, and then write-protected. Starting at the lowest address it stores the bootloader. It may also store application programs and/or special test programs. The bootloader FRAM cannot be changed by the user.

#### 5.5.2.4 User FRAM

This non-volatile memory will be delivered from the factory with the application program loaded. The program can be patched or replaced at any time using a sequence of POKE commands. This permits software updates after delivery, and even on-orbit.

#### 5.5.2.5 Application Images

Application image structures are stored in FRAM, to be loaded and executed by INIT commands. The format is:

| Offset | Length   | Function                                     |  |

|--------|----------|----------------------------------------------|--|

| 0x00   | 4        | RAM target address (32-bit unsigned integer) |  |

| 0x04   | 4        | Data length (32-bit unsigned integer)        |  |

| 0x08   | 4        | Start address (32-bit unsigned integer)      |  |

| OxOC   | Variable | 1 or more bytes of image data                |  |

Table 48: Application Image Structure

When an INIT command is executed on an application image the processor will copy a number of bytes equal to "Data length" from the "image data" field to the "RAM target address". It will then branch to the start address, which should be a pointer into RAM. In the special case that the start address is zero, no branch is made.

No integrity checks are made on the image format. Bad data (target address outside of RAM, data length too long, etc) will result in faults.

Two copies of the application image are stored on the wheel, one in the bootloader FRAM, one in the user FRAM. The image in the user FRAM is the preferred copy and is used when the wheel is initialized to address 0x20050000. The application image in the bootloader FRAM can be used by initializing to address 0x00002000.

#### 5.5.2.6 Error Mitigation

The RAM areas are protected from Single Event Upset (SEU) by hardware Error Correcting Codes (ECC). Each 8-bit byte is stored along with a 5-bit syndrome code. When the byte is read, the syndrome is re-calculated. Single-bit errors are automatically and transparently corrected and fixed. Multi-bit errors cannot be fixed. Both RAM areas are hardware scrubbed on a timescale of seconds.

The FRAM areas are protected by a hardware power switch. Whenever FRAM is not being used it is powered down. When FRAM is required the switch is turned ON and a 1 msec delay is observed before access. In typical orbital use the FRAM is turned ON for 380 msec after every reset, and is then OFF for normal operation.

#### 5.5.2.7 ECC Trap Words

The last words in the RAM areas have their ECC compromised, as the stored syndrome code is always '0'. When the stored word is '0', the ECC shows no errors. If a byte with a single '1' bit is written, a single-bit error is simulated. ECC hardware will correct the error. If a byte with two '1' bits is written, a multi-bit error is simulated. ECC hardware will count the error, but will be unable to correct it.

The trap words can be used on the ground for self-test purposes. These words should not be used for actual data storage.

### 5.5.3 Diagnostics

The diagnostics contain a series of read-only integers that relate to the health of the wheel.

Table 49: Diagnostic Channels

| Channel | Function                         | Format                              |

|---------|----------------------------------|-------------------------------------|

| 0x02    | Data RAM0 SEU count              | 16-bit unsigned integer x 2         |

|         |                                  | Low bytes: Single bit error count   |

|         |                                  | High bytes: Multi bit error count   |

| 0x03    | Program RAM SEU count            | 16-bit unsigned integer x 2         |

|         |                                  | Low 2 bytes: Single bit error count |

|         |                                  | High 2 bytes: Multi bit error count |

| 0x04    | Bootloader retries count         | Byte 0: 8-bit unsigned integer      |

|         | (from most recent reset)         | Bytes 1-3: '0'                      |

| 0x05    | Serial number                    | 32-bit unsigned integer             |

|         |                                  | Unique, but maybe not sequential    |

| 0x06    | FRAM status bytes                | Byte 0: Bootloader FRAM status      |

|         |                                  | Byte 1: User FRAM status            |

|         |                                  | Bytes 2-3: '0'                      |

| 0x07    | RS485-0 NSP Framing error count  | 32-bit unsigned integer             |

| 0x08    | RS485-0 Runt count               | 32-bit unsigned integer             |

| 0x09    | RS485-0 Oversize count           | 32-bit unsigned integer             |

| 0x0A    | RS485-0 Bad CRC count            | 32-bit unsigned integer             |

| 0x0B    | RS485-0 FIFO overflow count      | 32-bit unsigned integer             |

| 0x0C    | RS485-0 Incoming discarded count | 32-bit unsigned integer             |

| 0x0D    | RS485-0 Outgoing discarded count | 32-bit unsigned integer             |

| 0x0E    | RS485-1 NSP Framing error count  | 32-bit unsigned integer             |

| 0x0F    | RS485-1 Runt count               | 32-bit unsigned integer             |

| 0x10    | RS485-1 Oversize count           | 32-bit unsigned integer             |

| 0x11    | RS485-1 Bad CRC count            | 32-bit unsigned integer             |

| 0x12    | RS485-1 FIFO overflow count      | 32-bit unsigned integer             |

| 0x13    | RS485-1 Incoming discarded count | 32-bit unsigned integer             |

| 0x14    | RS485-1 Outgoing discarded count | 32-bit unsigned integer             |

| 0x1F    | Data RAM1 SEU count              | 16-bit unsigned integer x 2         |

|         |                                  | Low bytes: Single bit error count   |

|         |                                  | High bytes: Multi bit error count   |

| 0x20    | EF_ID1                           | 32-bit unsigned integer             |

| 0x21    | Uptime counter                   | Centi-sec (32-bit unsigned integer) |

| Channel | Function               | Format                  |

|---------|------------------------|-------------------------|

| 0x22    | RTC high word          | 32-bit unsigned integer |

| 0x23    | RS485-0 Incoming count | 32-bit unsigned integer |

| 0x24    | RS485-0 Outgoing count | 32-bit unsigned integer |

| 0x28    | RS485-1 Incoming count | 32-bit unsigned integer |

| 0x29    | RS485-1Outgoing count  | 32-bit unsigned integer |

FRAM status bytes can be expected as:

| Byte Value | Description                  |  |

|------------|------------------------------|--|

| 0x40       | FRAM chip is unlocked        |  |

| 0xCC       | FRAM chip is write-protected |  |

RS485 port error counters are zeroed at power-on and any reset

### 5.5.4 EDAC Memory

For historical reasons, the memory area used to store commands and telemetry is referred to as "EDAC Memory". In older wheels, this special area was subject to software-based triple-voting and scrubbing. In the new RW4 wheel every single flip-flop is protected against upset. There is no more or less protection for the EDAC Memory, but the name is preserved.

The memory area is 1536 bytes long. EDAC memory can be read with READ EDAC, GATHER EDAC and READ FILE commands, and written with WRITE EDAC and WRITE FILE commands. The MODE\_STORE command will save EDAC memory into non-volatile User FRAM. While the overlap between EDAC and FILE addresses is maintained for historical compatibility, it is recommended to use the READ\_FILE and WRITE\_FILE commands (rather than \*EDAC commands) for the floating-point values in the first 1024 bytes.

Table 50: EDAC Memory Contents

| EDAC Address  | File Address | Function       | Format                                   |

|---------------|--------------|----------------|------------------------------------------|

| 0x000 - 0x003 | 0x00         | Command Value  | Command Dependent                        |

| 0x00C - 0x00F | 0x03         | VBUS           | Volts (IEEE-754)                         |

| 0x01C - 0x01F | 0x07         | VDD            | Volts (IEEE-754)                         |

| 0x020 - 0x023 | 0x08         | VCC            | Volts (IEEE-754)                         |

| 0x024 - 0x027 | 0x09         | 6V             | Volts (IEEE-754)                         |

| 0x040 - 0x043 | 0x10         | TEMP0          | °C (IEEE-754)                            |

| 0x044 - 0x047 | 0x11         | TEMP1          | °C (IEEE-754)                            |

| 0x048 - 0x04B | 0x12         | TEMP2          | °C (IEEE-754)                            |

| 0x04C - 0x04F | 0x13         | TEMP3          | °C (IEEE-754)                            |

| 0x050 - 0x053 | 0x14         | TEMP_MCU       | °C (IEEE-754)                            |

| 0x054 - 0x057 | 0x15         | SPEED          | Rad/sec (IEEE-754)                       |

| 0x058 - 0x05B | 0x16         | MOMENTUM       | N-m/sec (IEEE-754)                       |

| 0x068 - 0x06B | 0x1A         | PWM            | Duty cycle (IEEE-754)                    |

| 0x06C - 0x06F | 0x1B         | HALL_DIGITAL   | Enum in IEEE-754 float                   |

| 0x080 - 0x083 | 0x20         | SPEED_P_GAIN   | Amps / rad / sec (IEEE-754)              |

| 0x084 - 0x087 | 0x21         | SPEED_I_GAIN   | Amps / rad (IEEE-754)                    |

| 0x088 - 0x08B | 0x22         | SPEED_D_GAIN   | Amps / rad / sec <sup>2</sup> (IEEE-754) |

| 0x094 - 0x097 | 0x25         | MAX_GAIN_SPEED | Rad/sec (IEEE-754)                       |

| 0x098 - 0x09B | 0x26         | MIN_GAIN_SPEED | Rad/sec (IEEE-754)                       |

| 0x0A0 - 0x0A3 | 0x28         | INERTIA        | kg-m² (IEEE-754)                         |

| EDAC Address  | File Address | Function               | Format                      |

|---------------|--------------|------------------------|-----------------------------|

| 0x0A4 - 0x0A7 | 0x29         | MOTOR_KT               | N-m/A (IEEE-754)            |

| 0x0A8 - 0x0AB | 0x2A         | GAIN SCHEDULE1         | (IEEE-754)                  |

| 0x0AC – 0x0AF | 0x2B         | GAIN SCHEDULE2         | (IEEE-754)                  |

| 0x0B0 - 0x0B3 | 0x2C         | GAIN SCHEDULE3         | (IEEE-754)                  |

| 0x0B4 - 0x0B7 | 0x2D         | GAIN SCHEDULE4         | (IEEE-754)                  |

| 0x0B8 - 0x0BB | 0x2E         | PROPORTIONAL OVERRIDE  | (IEEE-754)                  |

| 0x0BC - 0x0BF | 0x2F         | CONTROL TYPE           | (IEEE-754)                  |

| 0x0C8 - 0x0CB | 0x32         | MAX_SPEED_AGE          | sec (IEEE-754)              |

| 0x0CC - 0x0CF | 0x33         | LIMIT_SPEED            | Rad/sec (IEEE-754)          |

| 0x0D4 - 0x0D7 | 0x35         | LIMIT_CURRENT          | Amps (IEEE-754)             |

| 0x0E4 - 0x0E7 | 0x39         | MOTOR_RESISTANCE       | Ohms (IEEE-754)             |

| 0x0EC - 0x0EF | 0x3B         | SINUSOID_PHASE         | Rad (IEEE-754)              |

| 0x0F0 - 0x0F3 | 0x3C         | SINUSOID_FREQ          | Hz (IEEE-754)               |

| 0x0F4 - 0x0F7 | 0x3D         | SINUSOID_OFFSET        | Rad/sec or Volts (IEEE-754) |

| 0x100 - 0x103 | 0x40         | PREVIOUS_SPEED         | Rad/sec (IEEE-754)          |

| 0x104 - 0x107 | 0x41         | SPEED_INTEGRATOR       | Amps (IEEE-754)             |

| 0x108 - 0x10B | 0x42         | SPEED_LAST_ERROR       | Rad/sec (IEEE-754)          |

| 0x10C - 0x10F | 0x43         | ACCEL_TARGET           | Rad/sec (IEEE-754)          |

| 0x12C - 0x12F | 0x4B         | TORQUE_TO              | Nm (IEEE-754)               |

| 0x130 - 0x133 | 0x4C         | TORQUE_T1              | Nm (IEEE-754)               |

| 0x134 - 0x137 | 0x4D         | TORQUE_T2              | Nm (IEEE-754)               |

| 0x138 - 0x13B | 0x4E         | TORQUE_T3              | Nm (IEEE-754)               |

| 0x13C - 0x13F | 0x4F         | TORQUE_T4              | Nm (IEEE-754)               |

|               |              |                        |                             |

| 0x168 - 0x16B | 0x5A         | SLEEP_DUTY             | Fraction (IEEE-754)         |

| 0x16C - 0x16F | 0x5B         | DCDC_FREQ              | Hz (IEEE-754)               |

| 0x178 - 0x17B | 0x5E         | DRIVE_FREQ             | Hz (IEEE-754)               |

| 0x17C - 0x17F | 0x5F         | DCDC_SLOPE             |                             |

| 0x180 - 0x183 | 0x60         | DCDC_OFFSET            |                             |

| 0x184 - 0x187 | 0x61         | RESPONSE_AMPLITUDE     | Rad/sec (IEEE-754)          |

| 0x188 - 0x18B | 0x62         | RESPONSE_PHASE         | Rad (IEEE-754)              |

| 0x190 - 0x193 | 0x64         | KT_ESTIMATE            | N-m/A (IEEE-754)            |

| 0x194 - 0x197 | 0x65         | R_ESTIMATE             | Ohms (IEEE-754)             |

| 0x198 - 0x19B | 0x66         | DV_ESTIMATE            | Volts (IEEE-754)            |

| 0x19C - 0x19F | 0x67         | DRY_FRICTION_ESTIMATE  | Nm (IEEE-754)               |

| 0x1A0 - 0x1A3 | 0x68         | WET_FRICTION_ESTIMATE  | N-m/rad/sec (IEEE-754)      |

| 0x1A4 - 0x1A7 | 0x69         | AERO_FRICTION_ESTIMATE | N-m/rad²/sec² (IEEE-754)    |

| 0x1A8 - 0x1AB | 0x6A         | RUNDOWN_TIME           | sec (IEEE-754)              |

|               |              |                        |                             |

| 0x1C0 - 0x1C3 | 0x70         | FAULT_OVERTEMP0        | °C (IEEE-754)               |

| 0x1C4 - 0x1C7 | 0x71         | FAULT_UNDERTEMP2       | °C (IEEE-754)               |

| 0x1C8 - 0x1CB | 0x72         | FAULT_OVERTEMP3        | °C (IEEE-754)               |

| 0x1CC - 0x1CF | 0x73         | FAULT_TEMP_DELTA       | °C (IEEE-754)               |

| 0x1D0 - 0x1D3 | 0x74         | FAULT_OVERSPEED        | Rad/sec (IEEE-754)          |

| 0x1D4 - 0x1D4 | 0x75         | FAULT_OVERCURRENT      | Amps (IEEE-754)             |

|               |              |                        |                             |

| 0x200 - 0x203 | 0x80         | TEMP_R0                | Ohms (IEEE-754)             |

| 0x204 - 0x207 | 0x81         | TEMP_R2                | Ohms (IEEE-754)             |

| 0x208 - 0x20B | 0x82         | TEMP_R3                | Ohms (IEEE-754)             |

| EDAC Address  | File Address | Function         | Format              |

|---------------|--------------|------------------|---------------------|

| 0x20C - 0x20F | 0x83         | ADC_RAW_VBUS     | Ratio (IEEE-754)    |

|               |              |                  |                     |

| 0x3C0 - 0x3C3 | 0xF0         | RESERVED         | 32-bit unsigned int |

| 0x3C4 - 0x3C7 | 0xF1         | RESERVED         | 32-bit unsigned int |

| 0x3C8 - 0x3CB | 0xF2         | RESERVED         | 32-bit unsigned int |

|               |              |                  |                     |

| 0x5C3         |              | MODE             | 8-bit enum          |

| 0x5CE         |              | HALL_IMPOSSIBLE  | 8-bit unsigned int  |

| 0x5CF         |              | HALL_SKIP        | 8-bit unsigned int  |

| 0x5D0         |              | CONTROL_OVERFLOW | 8-bit unsigned int  |

| 0x5D1         |              | SPEED_TABLE_SIZE | 8-bit unsigned int  |

| 0x5D2         |              | USED_TABLE_SIZE  | 8-bit unsigned int  |

| 0x5D6         |              | IDLE_INHIBIT     | 8-bit boolean       |

| 0x5D7         |              | FLAGS_ACTIVE     | 8-bit bitmap        |

| 0x5D8         |              | FAULTS_MASK      | 8-bit bitmap        |

| 0x5D9         |              | FLAG_OVERTEMP0   | 8-bit boolean       |

| 0x5DA         |              | FLAG_UNDERTEMP2  | 8-bit boolean       |

| 0x5DB         |              | FLAG_OVERTEMP3   | 8-bit boolean       |

| 0x5DC         |              | FLAG_TEMP_DELTA  | 8-bit boolean       |

| 0x5DD         |              | FLAG_OVERSPEED   | 8-bit boolean       |

| 0x5DE         |              | FLAG_OVERCURRENT | 8-bit boolean       |

| 0x5DF         |              | FLAG_HALL_ERROR  | 8-bit boolean       |

| 0x5E0         |              | HALT             | 8-bit boolean       |

| 0x5E1         |              | RESET_ENABLE     | 8-bit bitmap        |

| 0x5E2         |              | RESERVED         | 8-bit bitmap        |

| 0x5E3         |              | STARTUP_DELAY    | 8-bit integer       |

| 0x5E4         |              | LOCKUP           | 8-bit boolean       |

#### 5.5.4.1 Command Value

Accessing file 0 causes an extra mode byte to be transferred. By writing to this file the mode of the wheel can be commanded. By reading this file the current mode can be determined.

If this parameter is accessed through EDAC writes and reads instead of file reads and writes there is no explicit mode byte transferred. It is possible to read and write the number associated with the command, but this is not advised.

#### 5.5.4.2 VBUS

This read-only parameter returns the voltage on the primary power bus. It is inferred by measuring the duty cycle of the DC/DC converter.

#### 5.5.4.3 VDD

This read-only parameter returns the voltage on the +1.6 V nominal secondary output from the DC/DC converter.

#### 5.5.4.4 VCC

This read-only parameter returns the voltage on the +3.3 V nominal secondary output from the DC/DC converter

#### 5.5.4.5 TEMP[0|1]

These read-only parameters return the temperature of the motor windings.

The sensors are NTC devices, so an open-circuit failure causes an apparent low temperature reading.

#### 5.5.4.6 TEMP[2|3]

These read-only parameters return temperatures on the circuit board. TEMP2 is located immediately next to the processor. TEMP3 is located adjacent to the motor drive transistors.

#### 5.5.4.7 TEMP\_MCU

This read-only parameter returns the temperature of the MCU. The sensor is internal to the MCU.

#### 5.5.4.8 SPEED

This read-only parameter returns the speed of the rotor.

#### **5.5.4.9 MOMENTUM**

This read-only parameter returns the angular momentum of the rotor. It is derived from the SPEED multiplied by INERTIA.

#### 5.5.4.10 PWM

This read-only parameter returns the commanded duty cycle of the PWM signal to the motor drivers.

#### 5.5.4.11 HALL\_DIGITAL

The wheel has three Hall-effect sensors (numbered 0 to 2), each one generating a binary value. The value of these three bits is encoded into this parameter.

| Hall 2 | Hall 1 | Hall 0 | HALL_DIGITAL |

|--------|--------|--------|--------------|

| 0      | 0      | 0      | 0.0          |

| 0      | 0      | 1      | 1.0          |

| 0      | 1      | 0      | 2.0          |

| 0      | 1      | 1      | 3.0          |

| 1      | 0      | 0      | 4.0          |

| 1      | 0      | 1      | 5.0          |

| 1      | 1      | 0      | 6.0          |

| 1      | 1      | 1      | 7.0          |

Table 51: Hall Digital Bitfield

#### 5.5.4.12 SPEED\_[P|I|D]\_GAIN

These read-only parameters set the gains for the PID closed-loop speed controller. See CONTROL\_TYPE for the formula to determine the gains.

#### 5.5.4.13 MIN\_GAIN\_SPEED, MAX\_GAIN\_SPEED

These read/write parameters bound the speed used as an input to the speed controller gain formula.

By setting these two parameters to the same value the speed dependence of the gains can be effectively disabled.

#### 5.5.4.14 INERTIA

This read/write parameter sets the rotor inertia. It is used to scale between acceleration and torque, and momentum and speed.

#### 5.5.4.15 MOTOR\_KT

This read/write parameter sets the motor torque constant.

#### 5.5.4.16 GAIN\_SCHEDULE[1..4]

These four read/write parameters are used to set the speed control gains, in those cases when PROPORTIONAL\_OVERRIDE is zero. First, the characteristic speed ② is determined based on the actual and setpoint speeds and on MAX\_GAIN\_SPEED and MIN\_GAIN\_SPEED.

$$\omega = MIN (MAX (|\omega_{actual}|, |\omega_{t \, arget}|, \omega_{MIN}), \omega_{MAX})$$

The critical gain and period are modeled as a function of the characteristic speed. The four GAIN\_SCHEDULE parameters are written as G1..G4.

$$Ku = G2 \cdot \omega^{G1}$$

$$Pu = G4 \cdot \omega^{G3}$$

#### 5.5.4.17 PROPORTIONAL\_OVERRIDE

This read/write parameter is used to override the gain settings, usually in a factory gain tuning context. When non-zero, the gains are set accordingly:

$$Kp = PROPORTIOML\_OVERRIDE$$

$$Ki = 0.0$$

$$Kd = 0.0$$

#### 5.5.4.18 CONTROL\_TYPE

This read/write parameter is used to determine the control type, using the Ziegler-Nichols method.

The value stored in CONTROL\_TYPE is truncated to an integer.

If the value is negative, then SPEED\_P\_GAIN, SPEED\_I\_GAIN and SPEED\_D\_GAIN are read-write parameters, set by the user.

If the value is 1, a PI controller is used:

$$Kp = 0.45 \cdot Ku$$

$$Ki = \frac{1.2 \cdot Kp}{Pu}$$

$$Kd = 0.0$$

If the value is 2, a PID controller is used:

$$Kp = 0.6 \cdot Ku$$

$$Ki = \frac{2.0 \cdot Kp}{Pu}$$

$$Kd = 0.125 \cdot KpPu$$

In the case of any other value, a P controller is used:

$Kp = 0.5 \cdot Ku$

Ki = 0.0

Kd = 0.0

#### 5.5.4.19 MAX\_SPEED\_AGE

This read/write parameter determines which digital Hall sensor transitions are used to determine the SPEED telemetry. Transitions are discarded if they are older than MAX\_SPEED\_AGE in time, if a complete rotor revolution has occurred since them, or if a rotor direction reversal is detected.

MAX\_SPEED\_AGE is relevant at very low rotor speeds. A larger value will allow more Hall sensor transitions to be used, giving a less noisy speed estimate. However, it will also increase the latency in speed measurements which may cause closed-loop speed control modes to become unstable.

#### 5.5.4.20 LIMIT SPEED

This read/write parameter sets the maximum speed that closed-loop modes will target. The magnitude of the speed target used in speed, torque, momentum and acceleration modes is clamped to this value. This is particularly significant in torque and acceleration modes – if communication with the flight computer is lost for any reason the rotor will slowly accelerate until this limit is reached.

#### 5.5.4.21 LIMIT\_CURRENT

This read/write parameter sets the greatest motor drive current used by closed-loop modes. Reducing this value will limit the torque that the wheel can generate.

#### 5.5.4.22 MOTOR\_RESISTANCE

This read/write parameter sets the motor nominal resistance.

#### 5.5.4.23 SINUSOID\_[PHASE, FREQ, OFFSET]

Please see SINUSOID mode for details

#### 5.5.4.24 PREVIOUS\_SPEED

This read-only parameter contains the SPEED file from the previous control frame. It is expected that it might be used in the future to generate torque telemetry, but at present it is unused.

#### 5.5.4.25 SPEED\_INTEGRATOR

This parameter contains the closed-loop controller integrator, scaled in amps of actuation. It is technically a read/write parameter, and it is possible for the user to write this for test purposes.

#### 5.5.4.26 SPEED\_LAST\_ERROR

This read-only parameter contains the controller error from the previous control frame. It is used with the differential gain term of the closed-loop controller.

#### 5.5.4.27 ACCEL\_TARGET

This parameter contains the speed setpoint used by the acceleration controller. The controller will add the acceleration to this file each frame. It is technically a read/write parameter, and it is possible for the user to write this as a way to force a new speed while remaining in acceleration/torque mode.

#### 5.5.4.28 TORQUE\_[T0..T4]

These five read-only parameters record the instantaneous torques measured in the last five control frames. To is the result of the most recent control frame. T4 is four frames old. The torque is computed as:

TORQUE = INERTIA \* (SPEED - PREVIOUS SPEED) \* 100 Hz

Torque telemetry at low speed should be used with caution. The speed estimate is only updated when new hall sensor pulses are seen (or a very long period elapses). If there has been no hall sensor pulse in the previous control frame then SPEED == PREVIOUS\_SPEED and so TORQUE == 0.

#### 5.5.4.29 SLEEP\_DUTY

This read-only parameter shows the fraction of the last 10 msec control frame that the processor has spent in the sleep mode. It provides a conservative measure of real-time margin.

A value of 1.0 would indicate continual sleep. A value of 0.0 would indicate that the processor is never sleeping, possibly due to the IDLE\_INHIBIT parameter.

#### 5.5.4.30 DCDC FREQ

This read-only parameter shows the frequency of the internal DC/DC converter, averaged over the last 10 cycles. The expected value is on the order of 100 kHz.

#### 5.5.4.31 DRIVE\_FREQ

This read/write parameter sets the switching frequency of the motor drive inverter. Permissible values are in the range of 100 kHz to 300 kHz.

As a special case, a value of 0.0 will synchronize the motor drive inverter to the DC/DC converter.

#### 5.5.4.32 DCDC SLOPE and DCDC OFFSET

These parameters determine the scaling between the observed DC/DC converter duty cycle and the VBUS telemetry.

#### 5.5.4.33 RESPONSE AMPLITUDE, RESPONSE PHASE

These read-only parameters are updated every time SINUSOID\_PHASE wraps around from 2½ to 0. They measure the speed oscillation that has resulted from a SINUSOID\_SPEED or SINUSOID\_VOLTAGE command.

RESPONSE AMPLITUDE is the amplitude of the speed sinusoid.

RESPONSE\_PHASE is the phase of the speed sinusoid with respect to the excitation sinusoid – expect a negative number which indicates a phase lag.

#### 5.5.4.34 KT\_ESTIMATE, R\_ESTIMATE

Every time that SINUSOID\_VOLTAGE updates RESPONSE\_AMPLITUDE and RESPONSE\_PHASE, these two read-only parameters are also updated. They are the values of motor KT and R that best fit the response sinusoid, given the INERTIA parameter that is assumed to be known.

The user must copy these values over to MOTOR\_KT and MOTOR\_RESISTANCE as part of an initial calibration operation — this is not done automatically.

#### 5.5.4.35 DRY FRICTION ESTIMATE, WET FRICTION ESTIMATE, AERO FRICTION ESTIMATE, RUNDOWN TIME

When the RUNDOWN mode completes, these read-only parameters are updated. The friction estimates are the best fit to the function:

TotalFriction=DryFriction+WetFriction\*speed+AeroFriction\* [speed] ^2

The sign of DRY\_FRICTION\_ESTIMATE is the same as the sign of the starting speed for the rundown. A rundown from a positive speed will result in a positive dry friction estimate, and a negative starting speed will result in a negative dry friction estimate. The wet friction estimate should always be positive.

RUNDOWN TIME measures the time, in seconds, for the wheel speed to reach zero.

#### 5.5.4.36 FAULT\_OVERTEMP[0|3]

These read/write parameters set the fault limits for TEMPO and TEMP3. If the temperature exceeds this threshold, even for a single measurement cycle, the corresponding fault flag will be set.

These limits detect overtemperature in the motor windings (channel 0) and the drive transistors (channel 3). These are areas that could be expected to get hot from continual high-torque operation.

#### 5.5.4.37 FAULT\_UNDERTEMP2

This read/write parameter set the fault limit for TEMP2. If the temperature is below this this threshold, even for a single measurement cycle, the corresponding fault flag will be set.

The limit detects undertemperature in the processor (channel 2). This is a proxy for bearing temperature, and can be used to prevent very low temperature startup.

#### 5.5.4.38 FAULT\_TEMP\_DELTA

This read/write parameter set the fault limit for the difference between TEMP2 and TEMP3. If the absolute value of this difference exceeds the threshold, even for a single measurement cycle, the corresponding fault flag will be set.